Sorting

Counters

n nodes: no IDs, or random ID' output: nodes have IDs 1,..., n, distinct

# Sorting

Counters

Frents

0 17

01/11/11

0 17

16

0 11 111

O (()

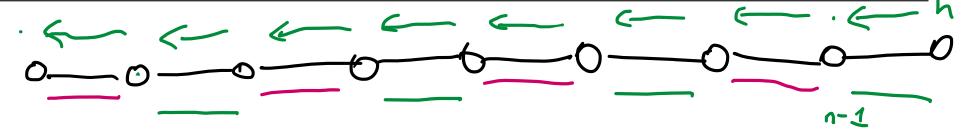

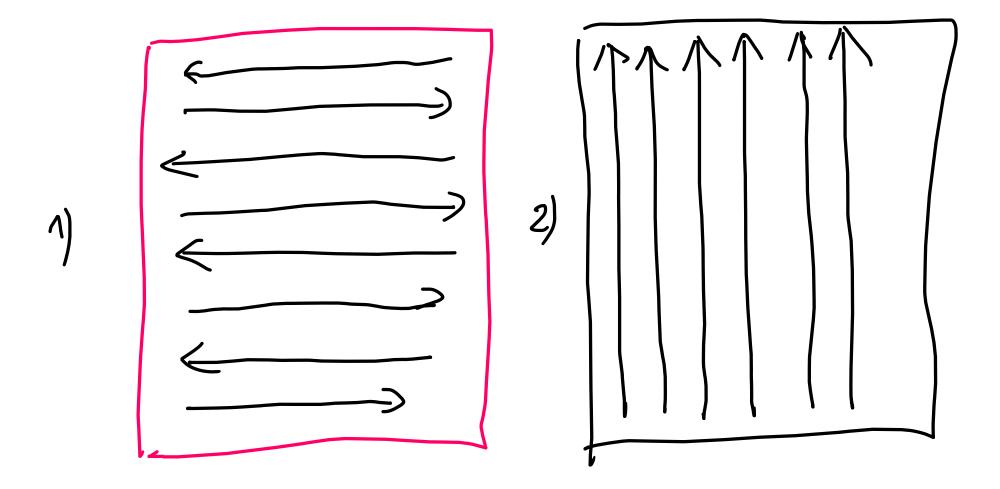

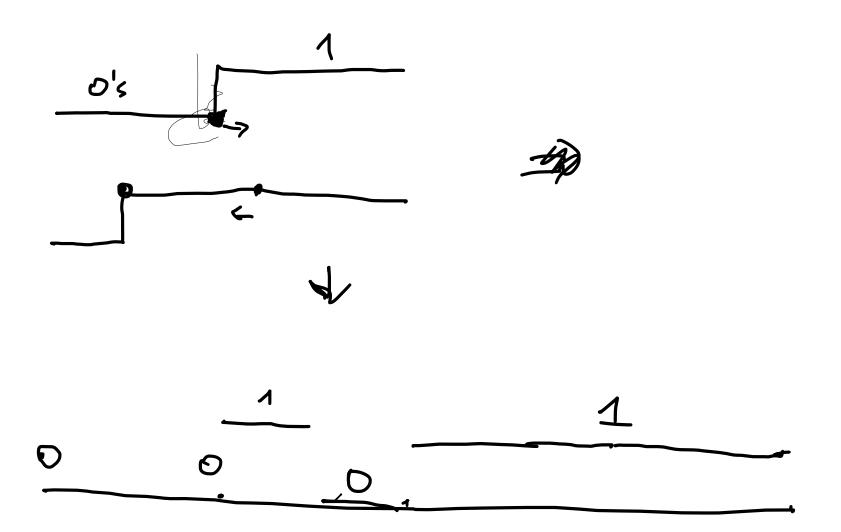

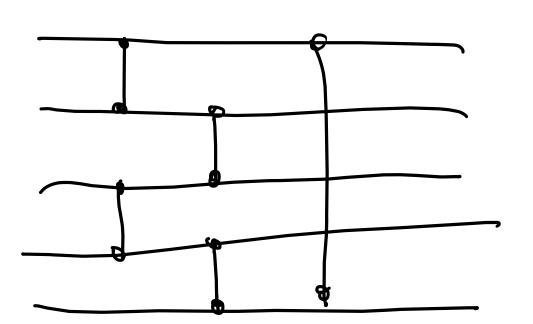

## Algorithm 4.3 Odd/Even Sort

- 1: Given an array of n nodes  $(v_1, \ldots, v_n)$ , each storing a value (not sorted).

- 2: repeat

- 3: Compare and exchange the values at nodes i and i + 1, i odd

- 4: Compare and exchange the values at nodes i and i + 1, i even

- 5: **until** done

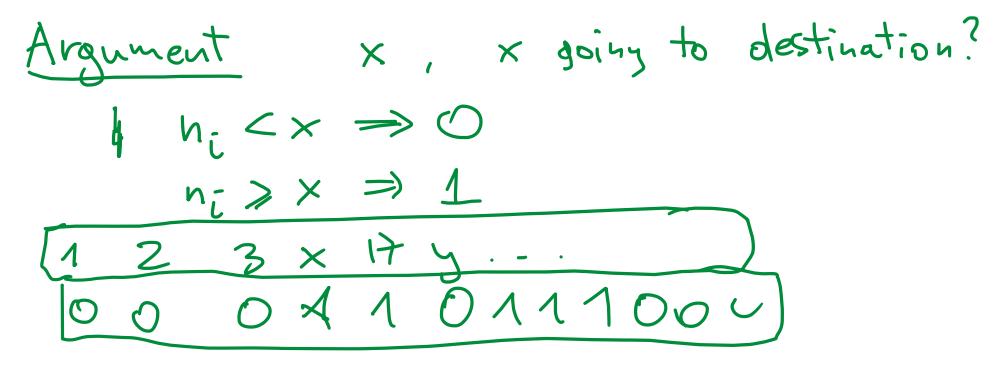

Lemma 4.4 (0-1 Sorting Lemma). If an oblivious comparison-exchange algorithm sorts all inputs of 0's and 1's, then it sorts arbitrary inputs.

010(1100)110(600 2 x 00000011111

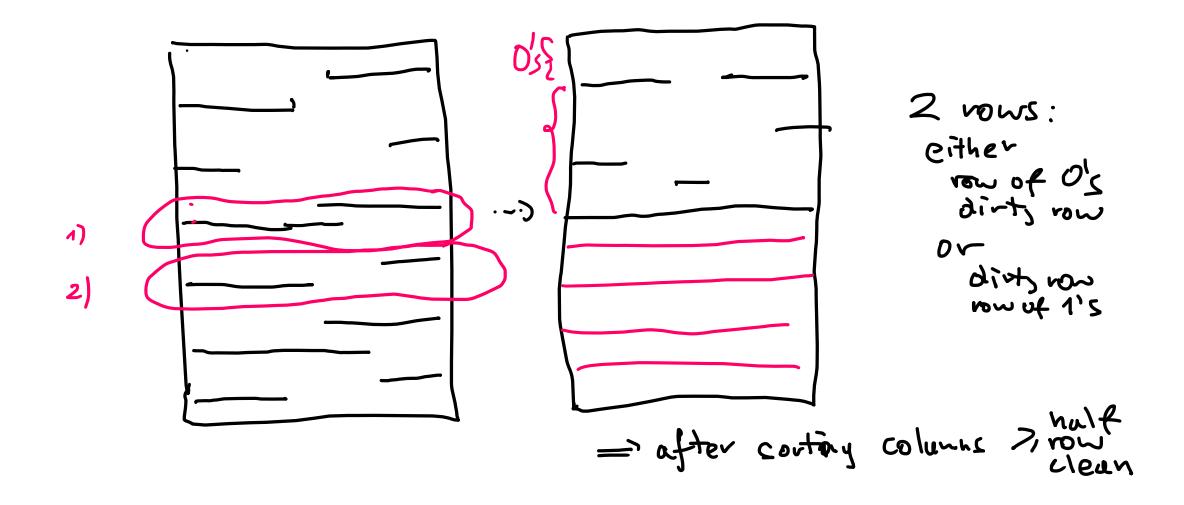

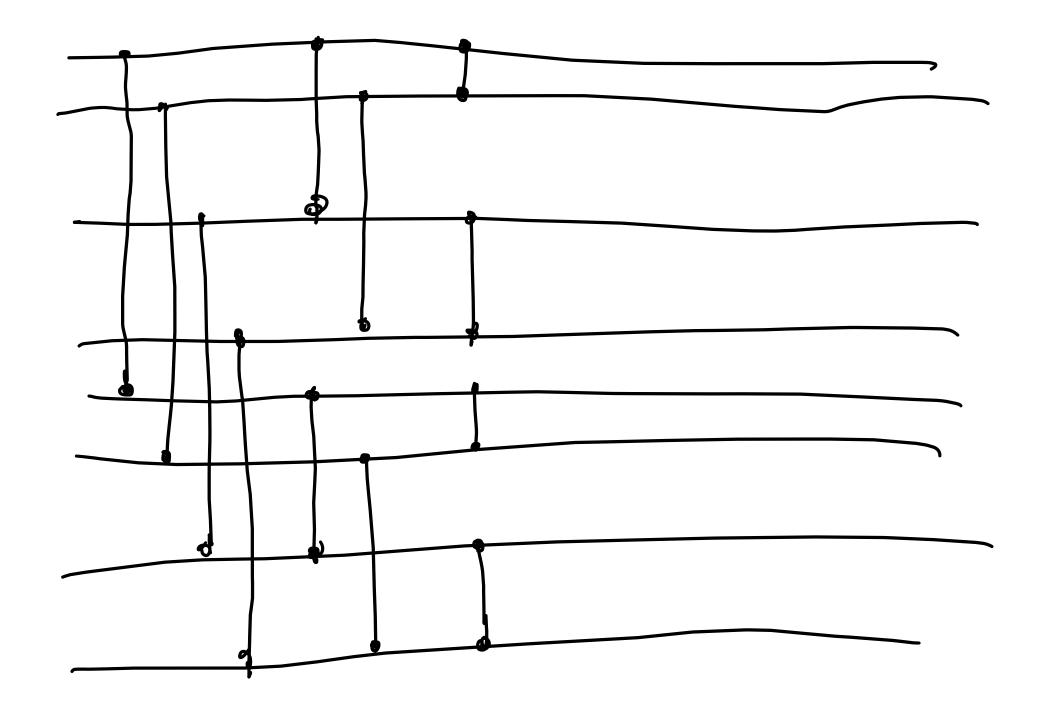

#### Algorithm 4.6 Shearsort

- 1: We are given a mesh with m rows and m columns, m even,  $n = m^2$ .

- 2: The sorting algorithm operates in phases, and uses the odd/even sort algorithm on rows or columns.

- 3: repeat

- 4: In the odd phases  $1, 3, \ldots$  we sort all the rows, in the even phases  $2, 4, \ldots$  we sort all the columns, such that:

- 5: Columns are sorted such that the small values move up.

- 6: Odd rows (1, 3, ..., m-1) are sorted such that small values move left.

- 7: Even rows (2, 4, ..., m) are sorted such that small values move right.

- 8: until done

•

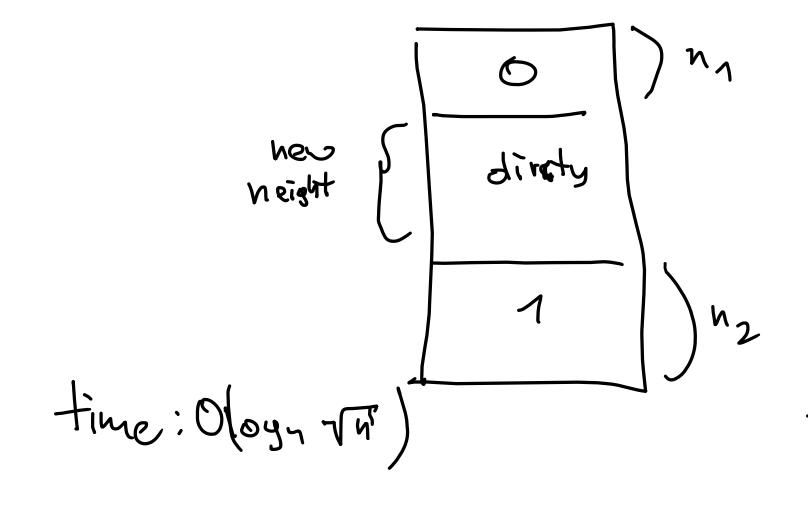

natnz > 1/2 height

logy rounds

# dirts rows = 1

hen 1 round terrinates

souting

2 din: 0(Vn. 10gn) shearsort un 3-dim. (ube improves! 0(3/4 logn) 4-dim., 5 bin...

Algorithm: periodic with constant period

period of length 3

repeat

1. ...

2. ...

3. ...

possible:

time ~ Vir. logs

Proof: JACK

**Theorem 4.7.** Algorithm 4.6 sorts n values in  $\sqrt{n}(\log n + 1)$  time in snake-like order.

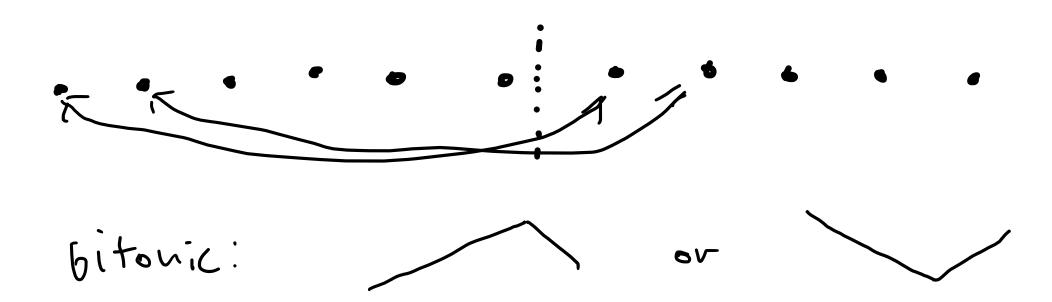

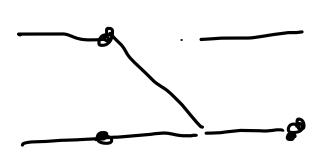

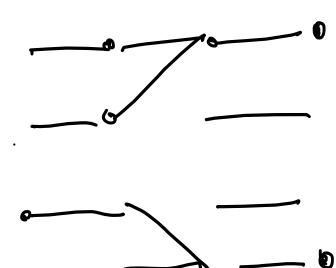

## Algorithm 4.12 Half Cleaner

1: A half cleaner is a comparison network of depth 1, where we compare wire i with wire i + n/2 for i = 1, ..., n/2 (we assume n to be even).

For bitouc inputs:

output: one hulf cleaned (sue value) one half bitain

### Algorithm 4.12 Half Cleaner

1: A half cleaner is a comparison network of depth 1, where we compare wire i with wire i + n/2 for i = 1, ..., n/2 (we assume n to be even).

For bitouc inputs: output: one hulf cleaned (sue value) one half bitain

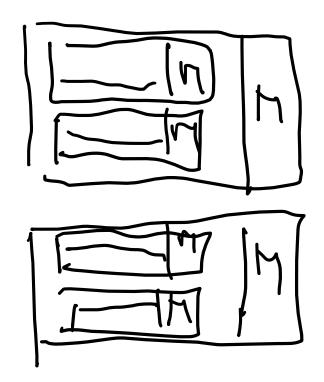

#### Algorithm 4.14 Bitonic Sequence Sorter

- 1: A bitonic sequence sorter of width n (n being a power of 2) consists of a half cleaner of width n, and then two bitonic sequence sorters of width n/2 each.

- 2: A bitonic sequence sorter of width 1 is empty.

- 1) bitton holf-cleaner of width n recursively: 2 bitonic Sequence Sorter

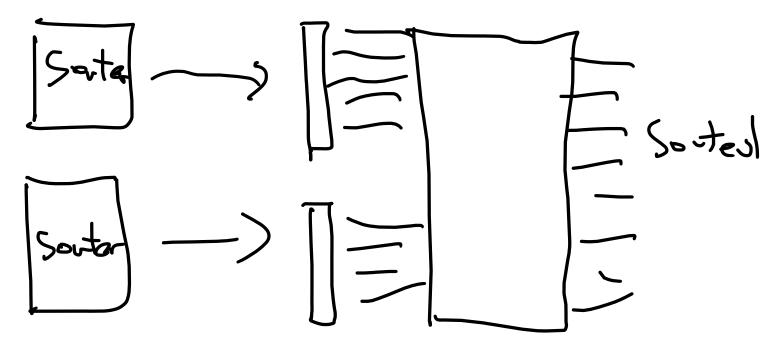

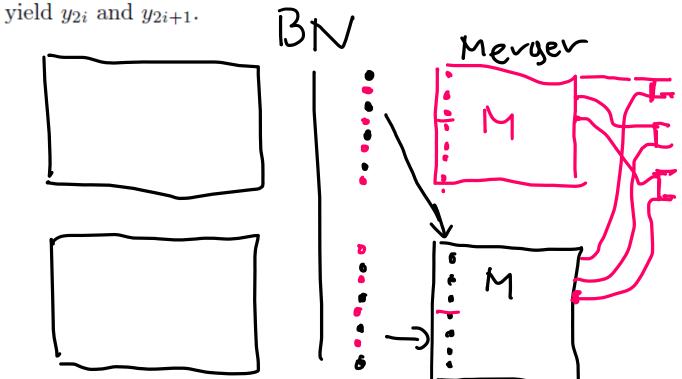

## Algorithm 4.16 Merging Network

1: A merging network of width n is a merger of width n followed by two bitonic sequence sorters of width n/2. A merger is a depth-one network where we compare wire i with wire n-i+1, for  $i=1,\ldots,n/2$ .

**Lemma 4.17.** A merging network of width n (Algorithm 4.16) merges two sorted input sequences of length n/2 each into one sorted sequence of length n.

## Algorithm 4.16 Merging Network

1: A merging network of width n is a merger of width n followed by two bitonic sequence sorters of width n/2. A merger is a depth-one network where we compare wire i with wire n-i+1, for  $i=1,\ldots,n/2$ .

**Lemma 4.17.** A merging network of width n (Algorithm 4.16) merges two sorted input sequences of length n/2 each into one sorted sequence of length n.

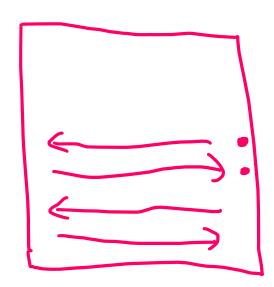

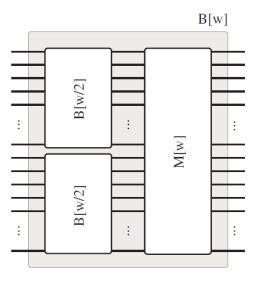

#### Algorithm 4.18 Batcher's "Bitonic" Sorting Network

- 1: A batcher sorting network of width n consists of two batcher sorting networks of width n/2 followed by a merging network of width n. (See Figure 4.19.)

- 2: A batcher sorting network of width 1 is empty.

Figure 4.19: A batcher sorting network

number of layers" is = log2n Mergen - O (logn) 109 n - depth of recursion

Intersting theoretical result:

I souting network of depth O (logn)

ALS Network

I mulos, Sze

nice: O(logn) & tousands of n

C. logn > log2n, for logn< c, n < 2 cabo

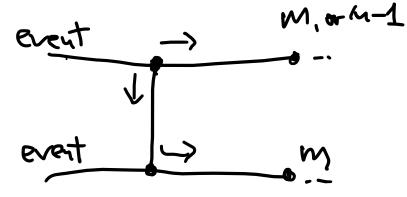

Distributed counting naire: central counter

Distributed counting naire: central counter

State

C2

C3

C4

C5

Car Ci = 3 ac acc = number of exects

balancer:

counter network:

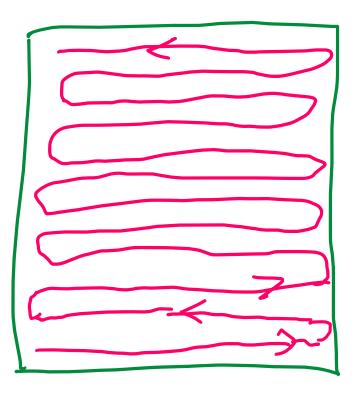

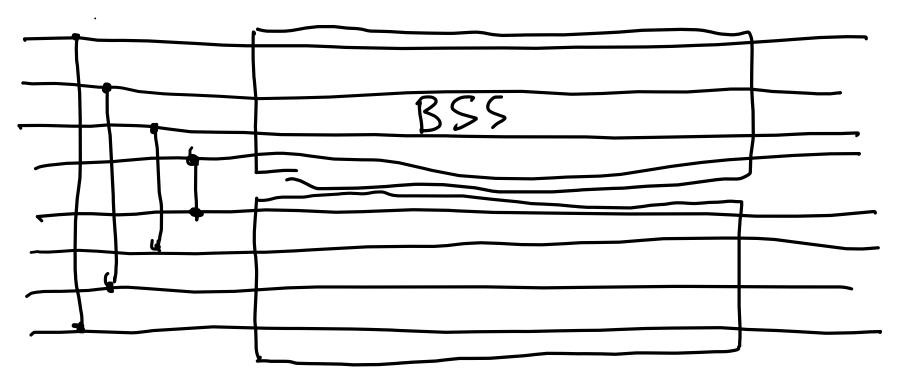

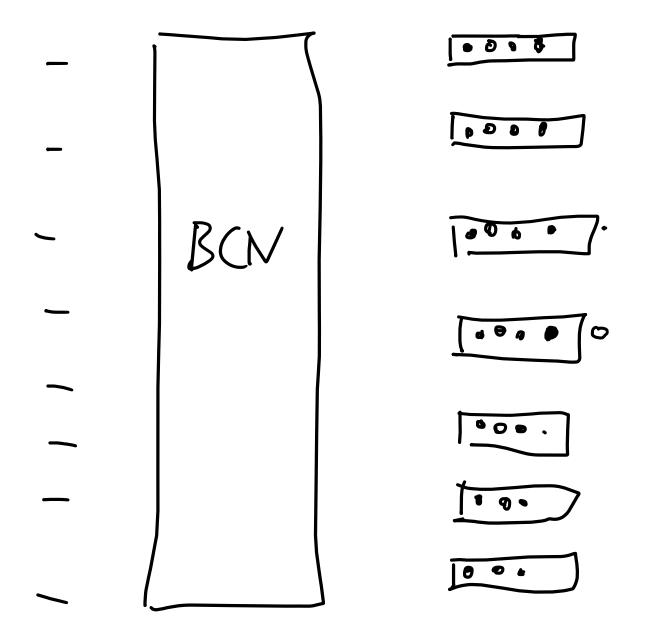

## Algorithm 4.23 Bitonic Counting Network.

- 1: Take Batcher's bitonic sorting network of width w and replace all the comparators with balancers.

- 2: When a node wants to count, it sends a message to an arbitrary input wire.

- 3: The message is then routed through the network, following the rules of the asynchronous balancers.

- 4: Each output wire is completed with a "mini-counter."

- 5: The mini-counter of wire k replies the value " $k + i \cdot w$ " to the initiator of the  $i^{th}$  message it receives.

| _ | BN | output, mini-counter for | <u>~</u> ) 5 |

|---|----|--------------------------|--------------|

| ~ |    |                          |              |

| - |    |                          |              |

| - |    |                          |              |

| _ |    |                          |              |

| _ |    |                          |              |

3·n+4< 194n+3

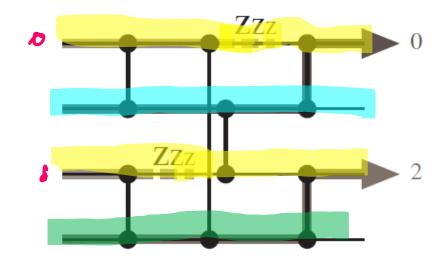

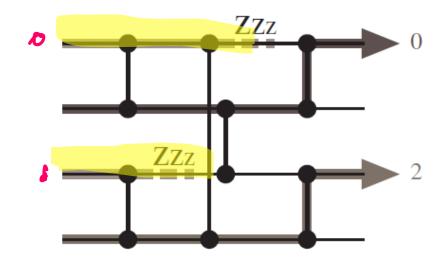

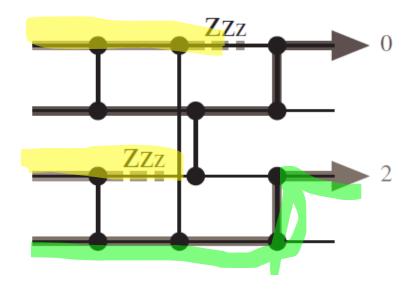

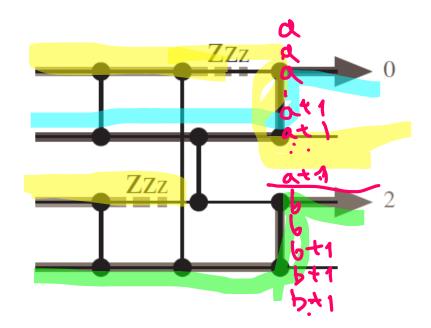

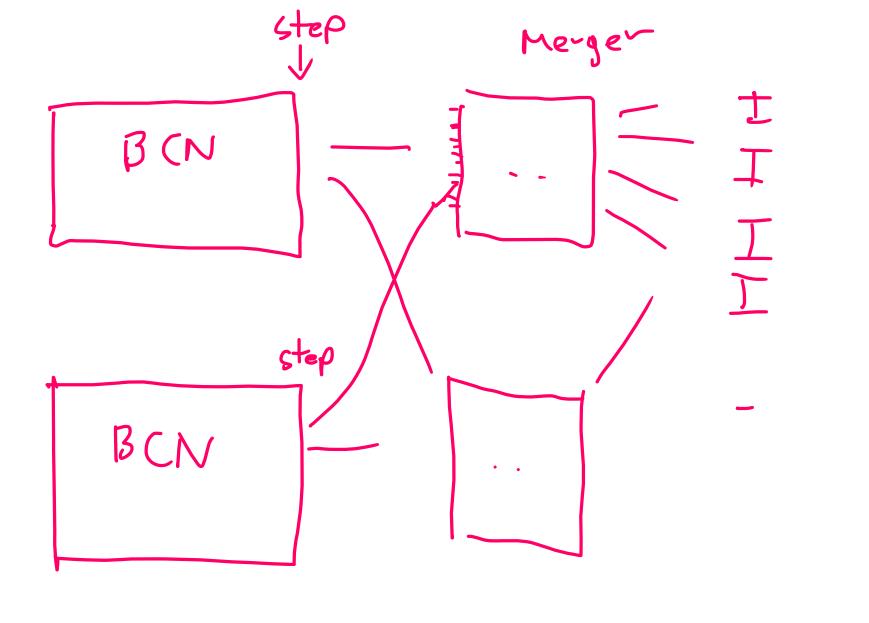

• An alternative representation of Batcher's network has been introduced in [AHS94]. It is isomorphic to Batcher's network, and relies on a Merger Network M[w] which is defined inductively: M[w] consists of two M[w/2] networks (an upper and a lower one) whose output is fed to w/2 balancers. The upper balancer merges the even subsequence  $x_0, x_2, \ldots, x_{w-2}$ , while the lower balancer merges the odd subsequence  $x_1, x_3, \ldots, x_{w-1}$ . Call the outputs of these two M[w/2], z and z' respectively. The final stage of the network combines z and z' by sending each pair of wires  $z_i$  and  $z'_i$  into a balancer whose outputs

Q B+ a 0, 0, 41 a cit1 a+1 D B b+1 b+1 4+ a at at 1 b 541 641 641 641 **H1**

**Definition 4.24** (Step Property). A sequence  $y_0, y_1, \ldots, y_{w-1}$  is said to have the step property, if  $0 \le y_i - y_j \le 1$ , for any i < j.

- 0 41 0

- = y, a

- 53 6

- · 54 at1

- at 1

**Lemma 4.28.** Let M[w] be a merger network of width w. In a quiescent state (no message in transit), if the inputs  $x_0, x_1, \ldots, x_{w/2-1}$  resp.  $x_{w/2}, x_{w/2+1}, \ldots, x_{w-1}$  have the step property, then the output  $y_0, y_1, \ldots, y_{w-1}$  has the step property.

Counting network >> sorting network Example: Obld-even Souter is not consten N asynchronous!